| 理想変成器を使って、トランスの等価回路を考える。トランスの基本機能を、理想変成器に置き換えることにより、トランス特性を各成分ごとに分けることが容易になる。実測した各成分をこの等価回路に当てはめることにより、実物特性により近い等価回路が得られる。等価回路例1〜3は、理想変成器と相互インダクタンスのみを表した等価回路。より詳細な等価回路を考える場合には、これに、鉄損(ヒステリシス損+渦電流損)、銅損(巻き線の抵抗分)、巻線間容量などを追加する(等価回路例4:ただし鉄損を線形として扱う)。また、ここではとり上げないが、SPICEなどのシミュレーションでは、鉄損を非線形要素として扱えるモデルも使われている。 |

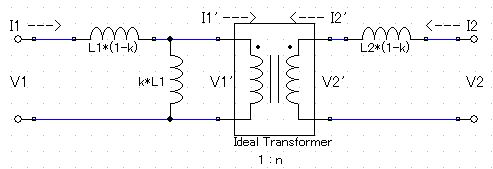

等価回路例1

(相互インダクタンスのみ)

|

この回路が式(6.8)と(6.9)を満たせば、正しい等価回路と言える。

V1=jωL1(1-k)I1+V1'

=jωL1(1-k)I1+jωkL1(I1-I1')

=jωL1(1-k)I1+jωkL1(I1+I2√(L2/L1))

=jωL1I1+jωMI2

V2=jωL2(1-k)I2+V2'

=jωL2(1-k)I2+√(L2/L1)V1'

=jωL2(1-k)I2+jωkL1(I1+I2√(L2/L1))√(L2/L1)

=jωL2I2+jωMI1

ただし、V2'/V1'=n=√(L2/L1)、I2/I1'=-√(L1/L2)、M=k√(L1L2)

|

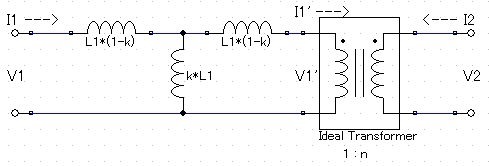

等価回路例2

(相互インダクタンスのみ)

|

この回路は、上記例1の2次側のインダクタンスを1/n^2して、1次側に換算したものである。換算法は、2次側に入っているインピーダンスは直並列に関係なく、1/n^2倍し(巻き数比1:n)、1次側にそのままの順番で平行移動する。R,Lは、それぞれ、R/n^2,L/n^2、Cは、Cn^2となることに注意。わざわざ片側に換算する理由は、実際のトランス特性を計測する場合に、1次側に換算していれば1次側からの測定だけで済ますことができるため(ネットワーク

・アナライザ等を用い、2次側を開放、短絡して測定)。

この回路が式(6.8)と(6.9)を満たせば、正しい等価回路と言える。

V1=jωL1(1-k)I1+jωkL1(I1-I1')

=jωL1(1-k)I1+jωkL1(I1+I2√(L2/L1))

=jωL1I1+jωMI2

また、V1=jωL1(1-k)I1+jωL1(1-k)I1'+V1'であるから

V1'=V1-jωL1(1-k)I1-jωL1(1-k)I1'

=jωL1I1+jωMI2-jωL1(1-k)I1-jωL1(1-k)(-I2√(L2/L1))

=jωkL1I1+jω√(L1L2)I2

V2=√(L2/L1)V1'

=jωk√(L1L2)I1+jωL2I2

=jωL2I2+jωMI1

ただし、V2/V1'=n=√(L2/L1)、I2/I1'=-√(L1/L2)、M=k√(L1L2)

|

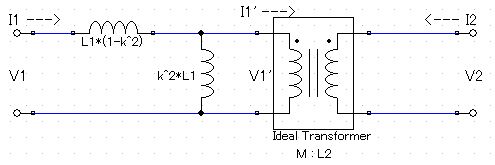

等価回路例3

(相互インダクタンスのみ)

|

上記の回路と同じ理由で、2次側特性(この場合2次側漏れインダクタンス)を1次側に換算している。

この回路が式(6.8)と(6.9)を満たせば、正しい等価回路と言える。

V1=jωL1(1-k^2)I1+V1'

=jωL1(1-k^2)I1+jωk^2L1(I1-I1')

=jωL1(1-k^2)I1+jωk^2L1(I1+L2I2/M)

=jωL1I1+jωMI2

V2=L2V1'/M

=jωk^2L1(I1+L2I2/M)L2/M

=(jωk^2L1L2I1+jωk^2L1L2^2I2/M)/M

=jωL2I2+jωMI1

ただし、V2/V1'=L2/M、I2/I1'=-M/L2、M=k√(L1L2)

|

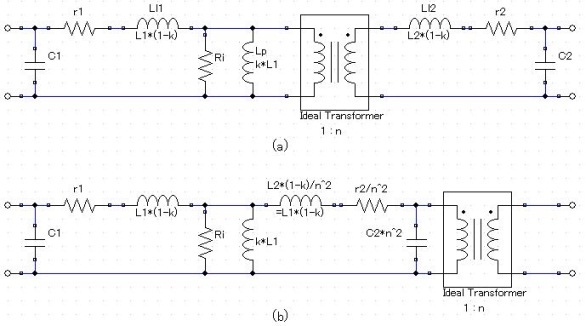

等価回路例4

(相互インダクタンス+その他)

|

図(a)の素子の意味

Lp:励磁インダクタンス、Ll1:1次巻き線漏れインダクタンス、Ll2:2次巻き線漏れインダクタンス、巻き数比N1:N2=1:n、

Ri:鉄損、r1:1次巻き線抵抗、r2:2次巻き線抵抗、C1:1次巻き線浮遊容量、C2:2次巻き線浮遊容量、

図(b)は、図(a)の2次側の素子を1次側に換算した場合。

|

SPICEによる確認: トランスのSPICE基本形とその他の等価回路

|

| SPICE回路図ファイル |

K_inductive_coupling_T.sch (TopSpice 8 回路図ファイル) |

.jpg) .jpg) クリックで拡大 クリックで拡大 |

| 回路図の作成 |

周波数50Hz、AC100Vを降圧する電源トランスをイメージした回路定数です。SPICEでトランスを構成するときの基本形と、これまで出てきた等価回路合計5種類を一つの回路図に入力しました。各種定数は、変更する場合に5回路分直すのが大変なので、.PARAMコマンドにより変数にしています。一箇所の定数を変更すれば、5回路分が同時に変わります。

SPICE基本形のトランスは、インダクタL素子二つと、インダクタ結合K素子で構成します。K素子において、どのインダクタ(2個以上可能)を結合させるかと、結合係数kを設定します(バークレーSPICE2、SPICE3では二つのインダクタしか結合できません)。これらのLとK素子は、回路図上でどこに配置しても機能上はかわりありませんが、図のようにそれらしく近づけて配置します。

サブサーキットX1〜X3は、理想変成器で、アナログ・ビヘイビア ・モデルです。従属電源で自分で作ることもできますが、ほとんどの商用SPICEにはライブラリに入っているはずです。

|

解析の設定と実行

(過渡解析)

|

定常時の波形を見るために、時間20ms〜80msとしています(0sの波形を気にしなければ、0〜60msでもかまいません)。正弦波なので、例によって最大時間ステップを60ms/1000=60usと設定します。信号源の初期位相90°とインダクタの初期電流IC=0Aは、第3章と同じ理由によります。 |

| 解析結果の検討 |

5回路の電圧電流がそれぞれ一致しているので、T型等価回路、理想変成器を使った等価回路の定数設定があっていることがわかります。電圧電流それぞれの振幅と位相関係も、式(6.24)〜(6.27)と合致した結果となっています。 |

SPICEによる確認: 全波整流回路(センタータップ型)

|

| SPICE回路図ファイル |

Full-Wave_Rectifier_test.sch (TopSpice 8 回路図ファイル) |

.jpg) .jpg) クリックで拡大 クリックで拡大 |

| 回路図の作成 |

巻き線が3本の場合の例として、センタータップ型全波整流回路をとり上げます。TopSpiceシミュレータのデモ版にも、同様の回路が添付されていますが、そちらはサブサーキットを使っています。その内部接続をL素子、K素子で書き換えました。

また、素子定数も一度で変更できるように変数化しています。ダイオードは、本講座の範疇を外れるものものですが、基本の整流機能を見るだけなので使用しました。ダイオードの特性を決めるモデル

・パラメータは、回路図内の.MODELコマンドで示されるように、指定なしであり、すべてデフォルト値が使われています。

なお全波整流回路としては、トランスにセンタータップが不要でネックとなるトランスの小型化に有利な、ブリッジ型全波整流回路の方がよく使われます。ダイオードが4つ必要ですが、4つが1パッケージに収められたブリッジ

・ダイオードが多く市販されています。

|

解析の設定と実行

(過渡解析)

|

定常時の波形を見るために、時間20ms〜60msとしています。正弦波なので、例によって最大時間ステップを40ms/1000=40usと設定します。信号源の初期位相90°とインダクタの初期電流IC=0Aは、第3章と同じ理由によります。 |

| 解析結果の検討 |

全波整流が正しく行われています。電圧電流それぞれの振幅と位相関係が、式(6.24)〜(6.27)と合致した結果となっています。

出力OUTに、平滑コンデンサを入力すると、DC出力が得られます。キャパシタの容量を変えて、リップルの変化を見たり、またキャパシタをより正確な等価回路で表したりと、実験が可能です。

|