TopSpice (Demo) 入門How to use TopSpice

7.モデルを自作して使う

最後に、簡単なSPICEモデルを自作して、解析してみましょう。

SPICEモデルは、使われる構文で大きく2種類に分けられます。.MODELコマンドで表される組み込みモデルと、ユーザーが組み込みモデルを自由に組み合わせて作る .SUBCKTコマンドで表されるサブサーキットです。

また、モデリングの手法としても大きく2種類に分けられると思います。SPICE誕生時の本来の目的である半導体設計用途の場合は、モデリングに際して、モデルをトランジスタレベルで実物に限りなく近づける必要がありますが、回路設計用途の場合は、中身はどうであれ(できればコンパクトである程良い)、目的の機能を持つモデルを用意できて、回路解析がうまくできれば良いことになります。

ここでは、サブサーキット構文によって、マクロ・モデルまたはビヘイビア・モデルといわれる、機能のみを再現するモデルを作ります。

言い換えると、前節まででは既成のOPアンプモデルを使っていましたが、この部分を、TopSpiceに組み込まれている関数や素子を組み合わせて、希望する機能を持つサブサーキットとしてモデル化します。

| Column [コラム] SPICEで使用されるモデルの分類 | ||

| 分 類 | 概 要 | 素子記号(TopSpice) |

| 組み込みモデル | 定数や参照素子名、関数式を入力すればよいモデル。 | C,E,F,G,H,I,K,L,R,T,V |

| 回路ファイル内で、別途.MODEL構文による記述をするか、その記述を含んだモデルライブラリを参照する必要があるモデル。そのモデル固有のモデルパラメータの設定が必要。SPICE内部に等価回路としてモデルが組み込まれている。 | B,C,D,K,M,O,Q,R,S,T,U | |

| サブサーキット | 構文.SUBCKT〜.ENDSで表され、組み込みモデルや別のサブサーキットを使って、ユーザーやデバイスメーカーが自由に構成できる回路ブロック。モデルライブラリとして保存することによって、別の回路ファイルから1つの回路ブロックまたはデバイスとして利用できる。大規模な回路図/回路ファイルを階層化して、分かりやすくする目的でも使われる。 | X |

| マクロモデル | 実際のICや回路をトランジスタレベルで忠実に再現しないで、制御電源などを用いて、理想化したり、伝達関数で機能を表したりして作るモデリング方法をマクロモデリングと呼び、できたモデルをマクロモデルと呼んでいる。複雑な回路もコンパクトに表せるので、シミュレーションの効率を上げることができる。 | X または組み込みモデルの組み合わせ |

前節で紹介したように、SPICEによるOPアンプモデルはメーカーより入手できますが、かなり規模が大きく、自分で手軽に特性を変更して実験してみるのは困難です。

SPICEでは、理想OPアンプは、電圧制御電圧源(VCVS)1個でできます。この基本形をベースに、自分で簡単に電圧利得、利得帯域幅積を指定できるようにしたモデルを作ってみます。(LTspiceの基本モデルを参考)

まず、順序はどちらでも構いませんが、作るモデルのシンボルを先に用意します。

ここでは前節と同じように前節で使った回路図をコピーし、変更しましょう。前節で作成したopamp2.schファイルを再度読み込んで、opamp30.schという別名で保存して下さい。メニューバーより

File>Save As

でopamp30.schを保存します。

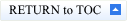

ここで、これから作成するモデルの特性に合わせて、入力信号源V1の波形をパルス波形から正弦波に変更しておきます。

| 図7-1 独立電圧源(電圧信号源)の設定 (過渡解析用) |

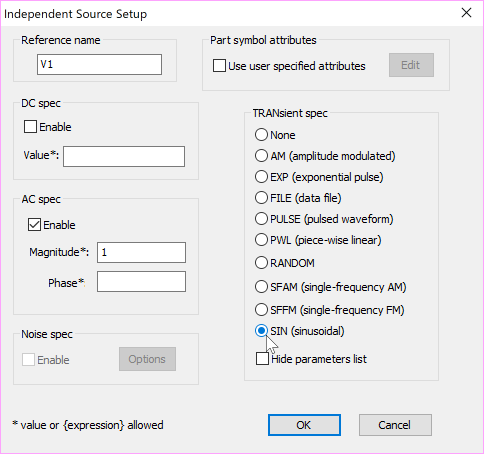

| 図7-2 正弦波のパラメータ設定 |

次に、X1,Vcc,Veeを選択してDeleteすることを繰り返して、この3つのシンボルを削除します。

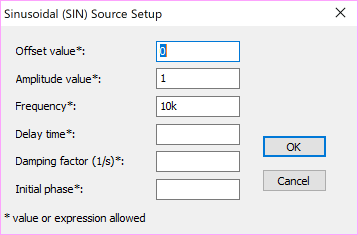

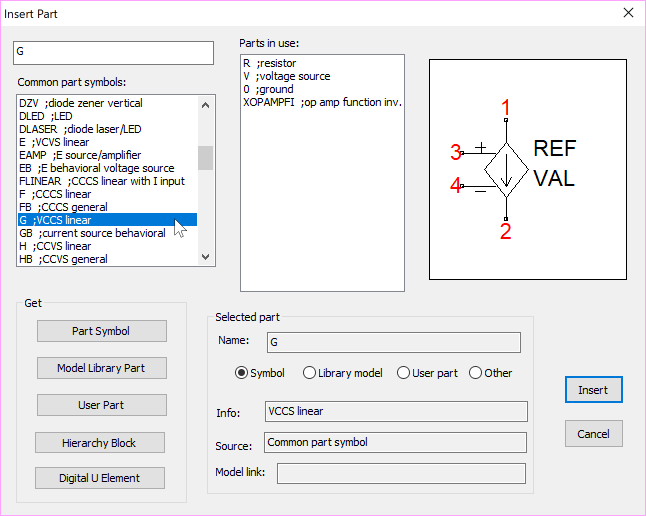

Insert>Part... または、ツール・バーの部品アイコンをクリックし

図7-3のように、電源ピンのないOPアンプのサブサーキット用シンボル"XOPAMPFI"を、選びます。

| 図7-3 電源ピンのないOPアンプのシンボルを選択 |

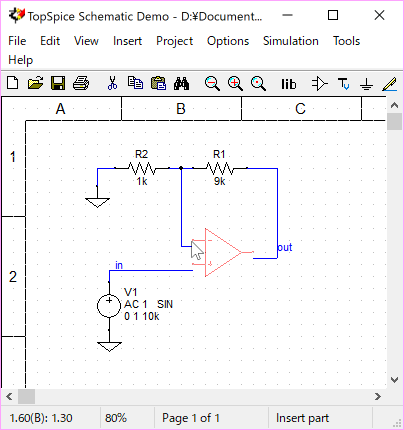

これを、図7-4のように、削除したX1の代わりに回路図に配置して下さい。

| 図7-4 回路図に配置する |

この時、今回は必要ありませんが、シンボルが選択されて赤くなっている状態で"F"キーを押すとシンボルの上下が反転して(Flip)そのまま回路図に当てはめることができます。(尚、90°回転(Rotate)は"R",左右反転(Mirror)は"M"です。)

この配置したシンボルはこの状態ではまだ、ピン付きのブラックボックスが回路図のノードに接続されたという意味しか表していません。

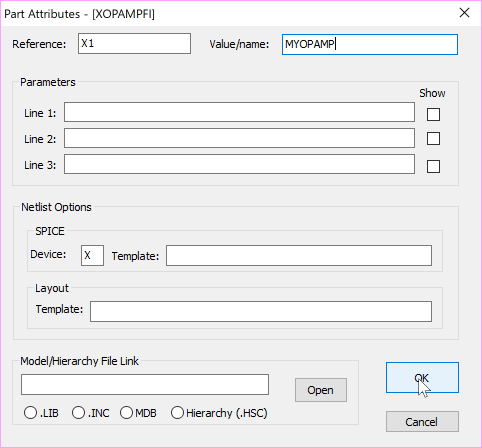

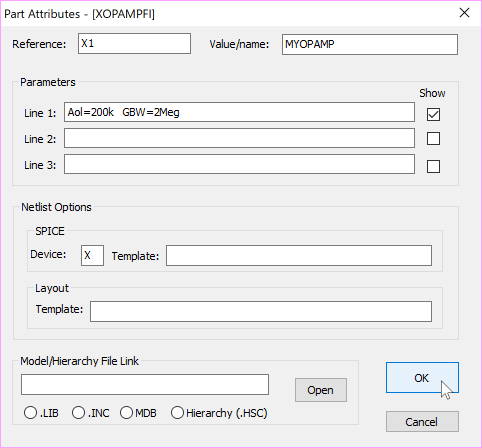

このシンボルの中身をサブサーキットで表し、モデル化します。X1シンボルをダブルクリックして開いたダイアログボックスで、ここでは、モデル名を「MYOPAMP」とします(図7-5)。

| 図7-5 サブサーキット・シンボル(X素子)にモデル名を入力する |

このシンボルの中身になるモデルは、全く別の回路図に作っても良いですし、同一回路図の2ページ目のシートに描いても良いですが、今回は小さな回路なので、同じシート上にサブサーキット回路図を描きます。他のSPICEにもある階層ブロックでも同様のことができますが、サブサーキットの内部を上位の回路図内に表示できるのは、TopSpice独自の機能といえます。なお、TopSpiceでは、階層ブロックの機能も別にあります。

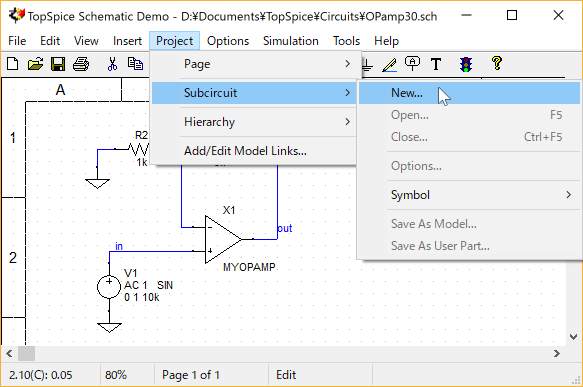

メニューバーより、図7-6のように

Project> Subcircuit > New...

とクリックして、

| 図7-6 サブサーキット回路図を作成開始 |

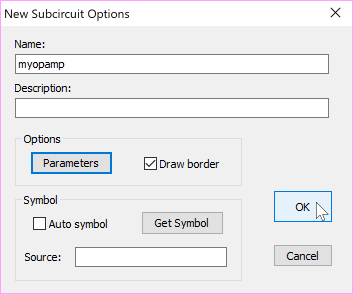

現れたダイアログボックスで、Name:欄に自分でモデル名を決めて入力して下さい。例として"MYOPAMP"と記入しました。Description:欄はメモ用のコメント欄です。シンボルは、既にシンボルライブラリから選び出していますので、一番下のAuto symbolのところのチェックを外しておきましょう(図7-7)。

| 図7-7 これから作成するサブサーキット名などの各種設定 |

OKをクリックすると、ステイタスバーにSUBCKT OPEN: MYOPAMPと表示され、サブサーキットの作成モードに入っていることが分かります。

このモードをCloseで閉じるまで、作成した回路図が、MYOPAMPという名前のサブサーキットになります。

Draw>Part...

Draw>Ground

Draw>I/O pin...

Draw>Wire

で図7-8〜図7-10のようにして、回路素子の選択と配置、定数の指定を繰り返し、サブサーキットの回路図を完成させます。

| 図7-8 電圧制御電流源Gを選択 |

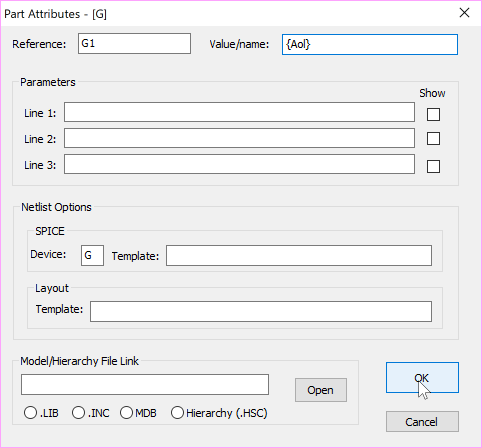

回路図に配置したG1(電圧制御電流源)をダブルクリックし、図7-9のようにパラメータ設定を行います。増幅度を変数「{Aol}」で指定します。この値を、後でケースバイケースで自由に指定できます。

| 図7-9 G素子の増幅度をパラメータ{Aol}とした |

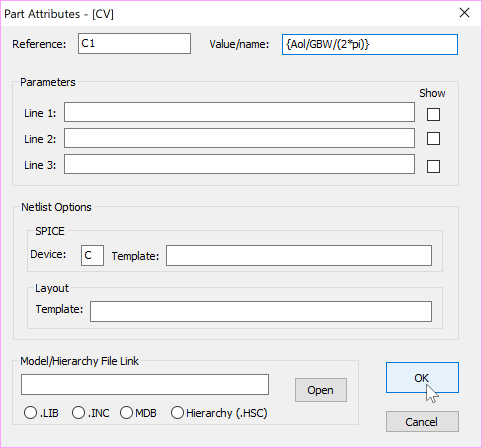

抵抗R1の値は、「1」とし、キャパシタC1の値は、「{Aol/GBW/(2*pi)}」とします。

| 図7-10 キャパシタ値を変数パラメータで設定する |

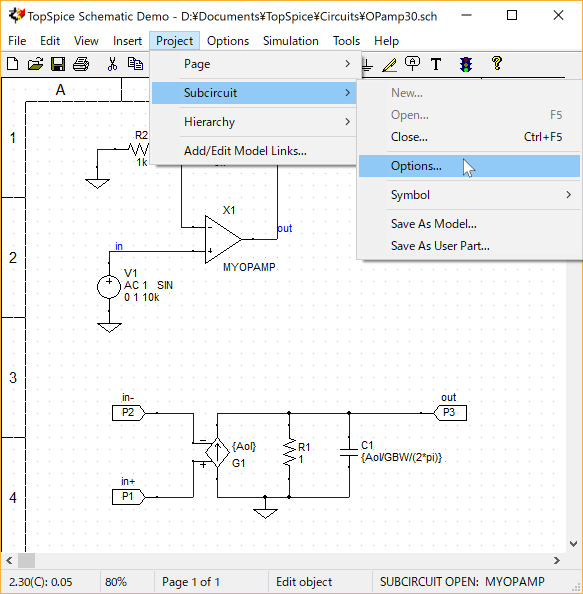

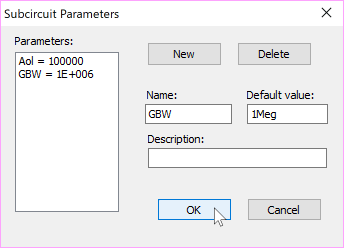

サブサーキットでは、図7-9と図7-10で設定したパラメータ変数の初期値を指定しておく必要があります。図7-11のようにOptionsをクリックし、図7-12のように設定します。

Project > Subcircuit > Options...

| 図7-11 サブサーキット回路図が完成したらパラメータを設定する |

| 図7-12 サブサーキットの初期パラメータ値を設定する |

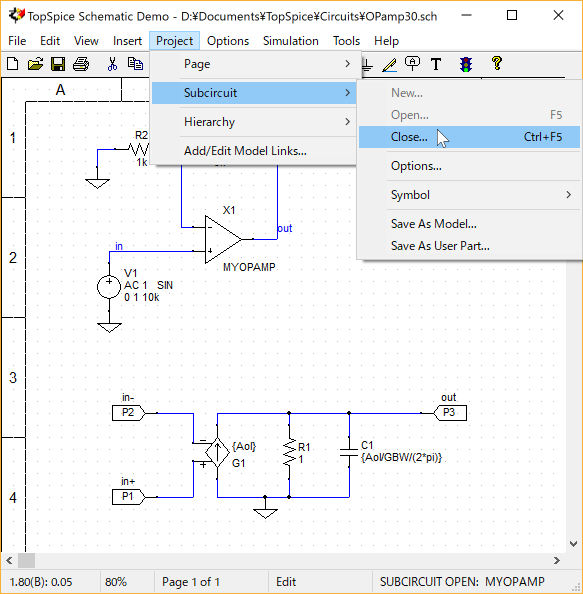

サブサーキットMYOPAMPの内部回路の作成、初期パラメータ値の設定が完了したら、サブサーキット作成モードの終了です。図7-13のようにして閉じて下さい。

Project > Subcircuit > Close...

| 図7-13 サブサーキットの作成モードを終了して閉じる |

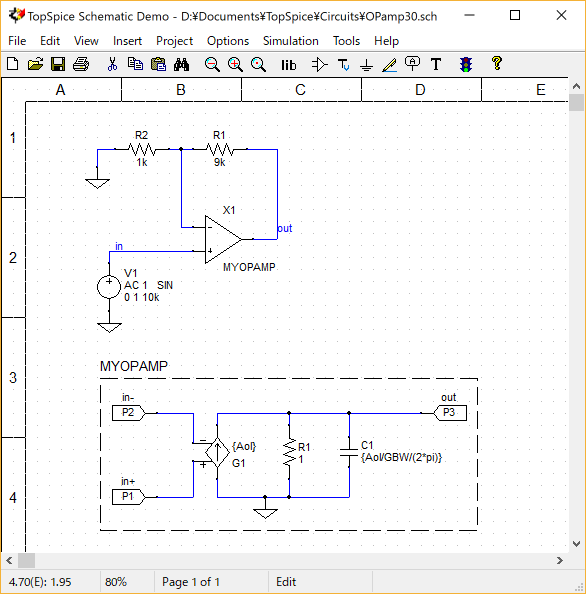

これで、シミュレーション用回路図の完成です(図7-14)。サブサーキット回路であることを示す点線が現れます。メイン回路図の素子X1(モデル名MYOPAMP)の内部が、展開されています。

| 図7-14 完成したシミュレーション回路図(展開されたサブサーキット回路図付き) |

これで今作成したモデルがこの回路図で使えるようになりました。解析の設定や観測ポイントの設定は、回路図のコピー時に引き継がれているので、基本的に新たに作成する必要はありません。

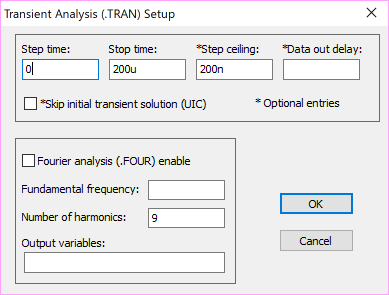

ただし、過渡解析で、ステップ上限値(Step ceiling)を設定しないと、ビヘイビア電源の動作上の理由で解析間隔時間が粗くなります。終了時間200usなので、経験上1/1000としてステップ上限値(Step ceiling)を200nsとします(図7-15)。なお、過渡解析の時間分割幅となるステップ時間(Step time)は、他のSPICEに合わせてTopSpiceでもデフォルトの「0」のままでも可となりました。

| 図7-15 過渡解析の設定のみ一部変更を加える |

このOPアンプモデルでは、パラメータとして「Aol」:電圧利得と「GBW」:利得帯域幅積が指定できます。図7-12で分かるように、これらのパラメータの初期値は、それぞれ100k(10万)倍、1MegHzとしています。

これらを変更したい場合は、初期値はそのままにして、メインの回路図のX1素子をダブルクリックして現れるダイアログボックスのParametersの欄に、希望の変数と値を入力します(図7-16)。

| 図7-16 サブサーキットのパラメータの指定方法 |

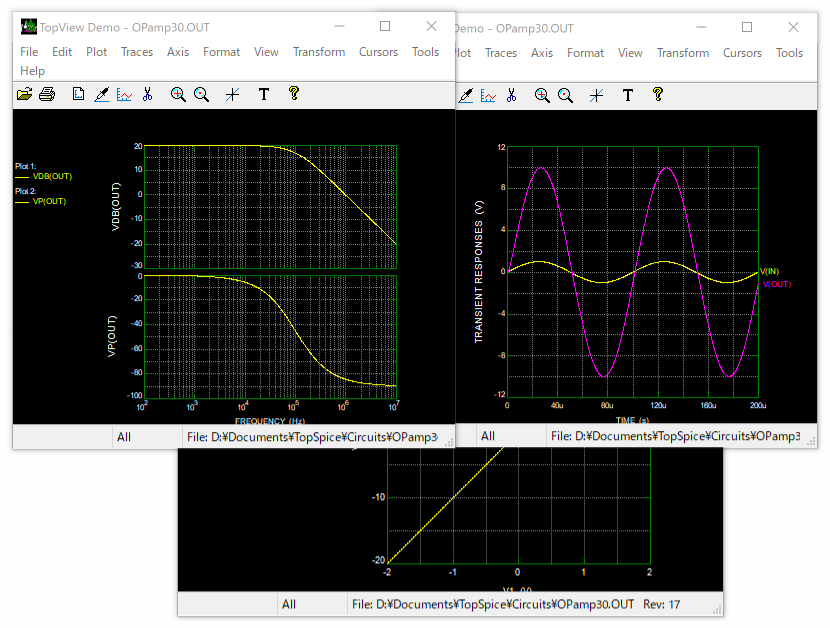

AC解析、過渡解析、DC解析をして、図7-17が得られます。

| 図7-17 解析結果(過渡解析,AC解析,DC解析) |

ここで作成した簡単なOPアンプのサブサーキット形式のモデルは、OPアンプのもっとも基本的な機能、つまり入力二端子を持ちその二端子間の電圧差を大きく増幅するという機能に加えて、位相補正された汎用のOPアンプが持つ基本的な周波数特性を再現しています。

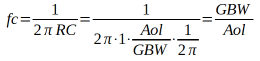

Aol:電圧利得(オープン・ループ・ゲイン、裸利得)とGBW:利得帯域幅積(≒ユニティ・ゲイン)というパラメータ値を、任意に設定して得られる一次ローパス特性を持っています。周波数特性が平坦部から利得が3dB低下(10・log(1/2)=-3.01dB)するカットオフ周波数(電力半値遮断周波数)fc は、RとCのインピーダンスが等しくなる周波数なので、以下の式で求めることができます。モデルのパラメータと比較すると意味も分かります。

8.SPICE回路シミュレータ使用時の注意点

SPICE回路シミュレータを使うとき、以下のポイントを覚えておくと非常に役に立ちます:

- SPICEは、トポロジー・エラー(SPICE規則に違反するものを除く)している回路は、解析しません。ユーザーが得る結果は、ユーザーの回路入力ファイルが正しい場合だけ「正しい」と言えます。もし、予想外の結果となった場合には、慎重にその回路記述をチェックして下さい。

- 大部分のデバイス・モデルは、デバイスの動作範囲内のある限られた範囲においてのみ正確です。もし、回路内のデバイスが「典型的な」動作範囲の外で動いているならば、ユーザーはモデルが正確かどうかも確認しなければなりません。

- 数値シミュレーションは、解法アルゴリズムにおいて、丸めのエラーと近似エラーを前提としています。これらのエラーは、長い時間のシミュレーション、回路サイズが非常大きい場合、大きなダイナミックレンジの回路の場合に累積する傾向があります。シミュレーション結果を分析するときは常に、懐疑的な態度を保つべきです。もし、シミュレーション出力が物理的に不可能であると思われるならば、おそらくその結果は間違っています。

- 実際の回路は、寄生的素子の影響を受けます。高い利得または高周波の回路における寄生的素子の影響は、回路のパフォーマンスと動作を支配するかもしれません。SPICEシミュレーションに含まれる寄生的素子の影響は、ユーザー自身がそれを回路に加えなければ観ることはできません。

- 信号波長が回路の物理的な大きさと同等または短くなるとき、その回路を正確にシミュレーションするには、分布定数回路としてモデル化しなければなりません。

一例として、TopSpiceでは、伝送線路、ラプラス変換、周波数レスポンス・テーブルとs-パラメータ・テーブルなどのSPICE素子を使って、分布定数回路を解析することができます。また、一体化(lumped)素子を使って、近似等価モデルを開発することもできます。 - SPICEは、電気的現象のシミュレータです。純粋に電気的でないシステム(モーターとランプのような)をシミュレーションすることは可能ですが、最初に非電気的なシステムを電気的に表すモデルを開発しなければなりません。

- 全ての回路電圧値は、グランド・ノードを基準として定められます。シミュレータ・グランド・ノードは、数学的なリファレンス・ポイントとしての意味のみを持ちます。アース・グランドと等しくはありません。

- 回路分岐電流は、SPICEシミュレーションにおいて直接は計算されません。全てのシミュレーション電流の出力値は、素子電流です。電流値の符号は、規則によって定義されます。電源においては、「正の」(第一の)端子から流れ出る電流は、負の値です。(電源内を+から−に流れる向きが正)他の2端子素子では、第一の端子に流れ込む電流が正の向きです。2つ以上の端子を持つ素子(例えばトランジスタ)では、あらゆる端子について流れ込む電流の向きが、正とされます。したがって、全ての素子の端子電流の合計は、ゼロとなります。